英特尔投下埃米炸弹:台积电的夸大宣传该到头了

作者| 宇多田

出品| 虎嗅科技组

封面| 视觉中国

自从去年英特尔被100%确凿证据证实了在10nm制程上的延期,以及在7nm制程上全面落后于台积电,丧失全球制程领导地位后,大众舆论对这家美国唯一从设计、制造到封测全覆盖的半导体企业的态度,呈现出惊人的一致变化:

除了竞争对手和看热闹不嫌事大一样的顺便踩一脚,这种“批判趋势”到最后似乎演变成——这家半导体顶级巨头剩下的日子似乎屈指可数了。

技术创新层面遭遇的危机也蔓延至他们的财务数据上,从2020年Q1到2021年Q3,英特尔净利润连续3个季度下滑;而历来作为数据中心市场的绝对王者,英特尔这一业务板块的收入也在三个季度内持续下降。

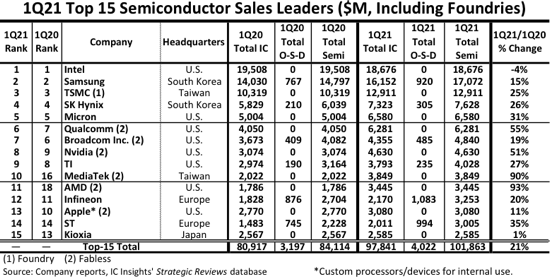

2021年5月,权威市场调研机构 IC Insights发布的《2021年Q1全球Top15半导体公司业绩与排名》指出,英格尔虽然位列第一,但却是所有厂商中唯一一家营收下滑的企业。

图片来自IC Insights

图片来自IC Insights

英特尔当然焦虑。这种焦虑可能体现在:

受到资本市场巨大压力,2021年年初突然换帅,重新启用有40年制造技术履历的帕特·基辛格(Pat Gelsinger)为新任CEO。

迅速接受了阿斯麦比自己更为先进的EUV制造工艺,用了大约两个季度的时间修复了7nm技术。

在制造环节投入巨资。今年3月,帕特·基辛格正式公布十分关键的“IDM 2.0”战略,宣布重返晶圆代工市场,同时宣布投资200亿美元在美国亚利桑那州新建两座晶圆厂;5月再次宣布,投资35亿美元升级新墨西哥州工厂,投资100亿美元在以色列兴建的芯片厂,还计划在欧盟建厂。

越来越多的英特尔半导体技术专家现身说法,为自己的制造技术正名,强调“每家晶圆厂的制程数据有对外宣传的差异”。

当然,根据虎嗅平台的观察和媒体反应,在国内大大小小的人工智能、物联网以及数据中心市场活动上,你能越来越多次看到英特尔出现的身影。

英特尔 CEO 帕特·基辛格

英特尔 CEO 帕特·基辛格

以重新夺回“制程节点”为目标的英特尔,今年3月发布的“IDM2.0战略”就以大手笔和”绝不放弃制造”的态度虽然引起产业重视,但因为表现不佳的财报状况持续受到争议;

而昨天,包括CEO基辛格在内的4位英特尔高级制造技术专家,再次通过大范围公开英特尔的制程技术和实现路径,向半导体产业投掷了一枚“新炸弹”:

英特尔的确在10nm和7nm有所延迟(如果感兴趣,可以看我的这篇文章《英特尔退位,台积电称王》),但在5nm节点上,英特尔自认为非但没有延迟,反而会完成超越。

为了应对台积电等对手的“制程虚假宣传”,以及纠正大家对制程的认知误区,英特尔直接舍弃了“10nm,7nm,5nm,3nm”这一本质上由摩尔定律决定的说法,而是直接采用100%英特尔主观视角的新命名体系——Intel7,Intel4,Intel3,Intel20A,Intel18A。

这一次公开的Intel20A,本质对应的就是5nm制程。这是一个英特尔近2年来闭口不谈的制程节点,相关时间计划基本到7nm就戛然截止了。英特尔首次宣布将通过Intel20A,进入“埃米时代”。

Intel20A背后两大关键技术非常值得注意。其中,这个制程将会采用全新的晶体管结构Gate-All-Around,并非是为22nm以下制程产品化立下汗马功劳的FinFET结构。

换言之,这种应用了新材料的新结构芯片,将会对传统制程概念,产生重大改变。就如一位半导体技术专家告诉虎嗅:“这种新的材料结构,制程这些几纳米啥的就没那么大的关系了。”

英特尔新制程命名体系:快醒醒,客户们

关于制程的命名问题,被产业诟病已久。

譬如我们曾在《英特尔退位,台积电称王》这篇文章里提及,业内不少工程师认为,英特尔在对待“纳米”制程数字的态度更实在,甚至表示“英特尔的10nm芯片对标的其实是台积电的7nm,甚至比后者的7nm都好”。

这也是基辛格上任后,多次在公开场合呼吁大家正确理解“制程数字”:

“包括英特尔在内,使用着各不相同的制程节点命名和编号方案,这些方案既不指代任何具体的度量方法,也无法全面展现如何实现芯片能效和性能的最佳平衡。”

这就像是车展上那些号称自己芯片达到几百几千Tops的汽车,也像是加州每年发布的《自动驾驶接管报告》——没有统一测试条件和足够的企业诚信度,就绝对不配说出“谁比谁性能好”的结论。

所以,英特尔这次兴师动众地更换了命名体系,美名曰:“让客户对整个行业的制程节点演进有一个更准确认知,进而做出更明智的决策”,其实主要目的就是对付台积电和三星不那么太靠谱的5nm和3nm制程名字。

2021年下半年将推出的Intel 7 (是不是至少看起来像是7nm?),其实就是英特尔之前发布的10nm Enhanced SuperFin;

2023年上半年发布的Intel 4(至少看起来像4nm?),其实就是英特尔之前PPT的7nm;

2023年下半年发布的Intel3,其实就是英特尔之前PPT上的7nm+;

2024年上半年发布的Intel20A(看起来像不像2nm?),其实就是英特尔标准下的5nm;

2025年上半年发布Intel18A,其实就是英特尔标准下的5nm+。

图片来自英特尔

图片来自英特尔

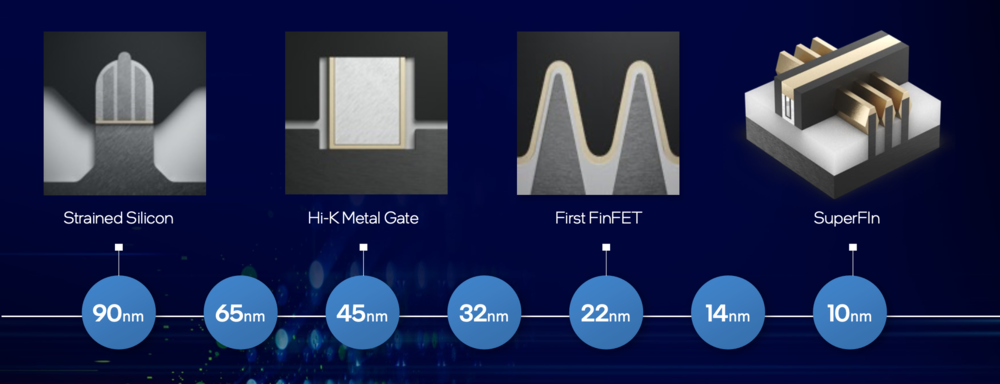

实际上,随着晶体管结构的愈加复杂,早在21世纪初,产业内就开始对芯片的纳米制程命名有了“分化趋势”。

我们都清楚,微处理器是由以特定方式连接起来的数十亿晶体管组成。这些晶体管充当了“开关”的角色,负责处理电子数据的1和0。

基辛格解释,在晶体管顶部有一个区域叫“栅极”,它决定了晶体管是开启还是关闭。而“制程节点”指代的是晶体管所需的数千个制造步骤组成的复杂方案。

而所有最顶级半导体公司几乎都有同一个目标——让这些芯片变得更小、更快、更便宜、更高能效——最好的例子莫过于苹果的5nm制程芯片M1(有太多关于M1的测评可以去看,我也买了一台M1的Macbook Air,爱不释手)。

最初,制程工艺“节点”的名称与晶体管的栅极长度相对应,并以“微米”为度量单位。随着晶体管越变越小,栅极的长度越来越微缩,产业开始以纳米为度量单位。

而关于制程命名改变的关键节点出现在1997年。

“随着技术进步和应变硅(strained silicon)等其他创新技术的出现,除了缩小晶体管,更快、更便宜和更高能效也变得同样重要。” 基辛格认为,从这时开始,传统命名方法不再与实际的晶体管栅极长度相匹配。

换言之,晶体管尺寸在某种程度上不是唯一的决定因素,它们之间的“互连”等因素也不能忽略。

2011年,在英特尔推出FinFET晶体管结构技术后,行业进一步分化。这是一种构建晶体管的全新方式,具有独特的形状和结构。

这个结构就是将停滞不前的22nm继续往下缩进的关键技术。但要很显然,从22nm开始,不要说大众,就连产业内对制程数字的理解与它的实际“坐标”也开始逐渐脱离。

这也是英特尔如今建立新命名体系的根本缘由。

正如虎嗅之前在采访工程师时得到的答案:“英特尔在制造工艺标准制定上相对更激进,要求也更高。但的确制程延迟了1~2年,说落后并不意味着他们没有追赶的可能性。”

但英特尔这次大刀阔斧的制程更名,也许不是不相信自己,而是嗅到了市场和资本已经被“命名”困惑已久(譬如开头),甚至依此来做出商务判断的残酷现实。

不过我们想到了一个问题——即便推出了新命名产品,客户没有理由不问一句:“你这intel7到底几纳米?对标的是台积电的几纳米?”

说实话,我们更想知道英特尔在遇到这个问题时怎么回答。

誓死捍卫摩尔定律?

基辛格在这次可谓是极为详尽的“制程技术科普会”上,至少提了三次关于“摩尔定律不会消亡,英特尔会通过各种方法,如改材料、晶体管结构,以及封装等角度,继续来延续摩尔定律”的决心。

实话讲,除了这个意味深长的新命名体系,英特尔最有趣且最应该受到关注的产品,毫无疑问是Intel3之后的Intel20A。

(当然,Intel4 将作为第一批应用阿斯麦高数值孔径(High-NA)极紫外辐射光刻技术(EUV)的处理器也倍受瞩目,但象征意义不如Intel20A。)

Intel 20A(5nm)之所以被英特尔称为历史上制程技术发展的下一个分水岭,是因为它是第一块应用英特尔两大“开创性技术”的芯片:

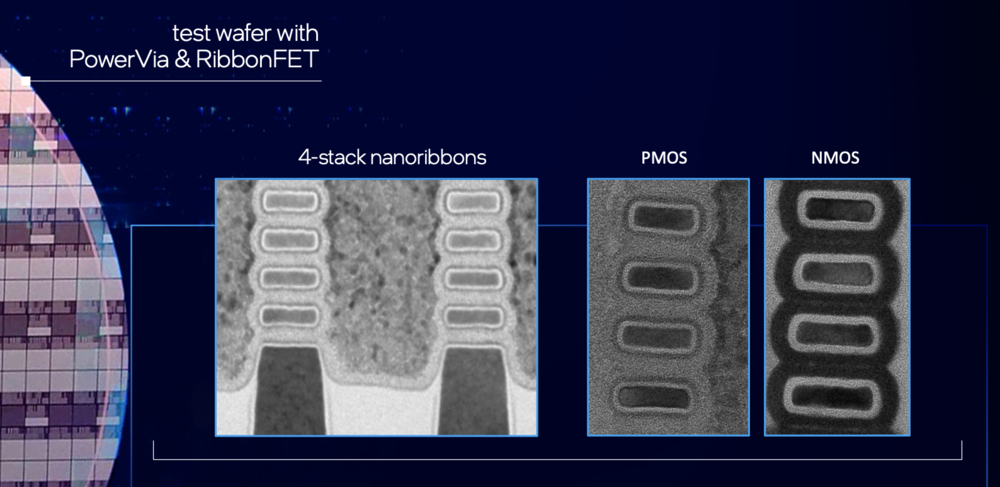

替代FinFET的全新晶体管架构 Gate-All-Around(英特尔把它命名为RibbonFET)

能够解决“互联瓶颈”的电能传输系统PowerVia。

FinFET技术的重要性已经无须赘述。

它是加州伯克利大学电子工程与计算机专业教授胡正明在1999年研发出的 3D 晶体管技术(鳍型晶体管)。英特尔之所以能在 12 年后率先量产出 22nm 晶体管,台积电与三星顺利过渡至 16/14nm 制程节点,FinFET功不可没。

正是这项“发明”,摩尔定律才得以“延寿”数十年。

但是,随着制程从5nm持续缩进至3nm,半导体制造专家们发现,进一步减少 FinFET 尺寸,就越来越受到驱动电流和静电控制的限制。

而将要替代它的Gate All Around的常用名为GAAFET(全栅场效应管),它使用栅极包围的带状通道,从而能实现更快的晶体管切换速度和更好的控制。因此,在更小的占用空间内,可具备更高的性能。三星在2020年曾宣布将在3nm制程芯片上应用这一架构。

图片来自泛林半导体

与 FinFET不同的是,在 FinFET 中,较高电流需要多个并排的鳍片;GAA 晶体管的载流能力主要是通过垂直堆叠几个纳米片(上图),而栅极材料主要是包裹在沟道周围来提高的。纳米片的尺寸可以按比例缩放,以便晶体管可以按照要求的特定性能进行调整。

听起来,“纳米片”的概念其实理解起来并不是那么困难;而且实际上,这项技术已经被研发多年。但其之所以不受业内“重用”,主要瓶颈就在于“材料”。

根据泛林半导体给出的解释,GAA晶体管是通过“交替硅”和“硅锗外延层”的超晶格来制作的,这是构成纳米片的基础,此外制作工艺相对复杂,可能需要钌、钼、镍等各种合金新材料进行沉积、蚀刻、填充。

一位半导体专家这样给虎嗅总结:“它(GAA)将对半导体的基底材料进行更改,半导体连接的材料也要进行更改。同时整个晶体管的物理结构也要变化。”

因此,带领团队开发这项技术的Sanjay Natarajan博士将英特尔的GAA——RibbonFET称为一次“晶体管性能上的重大飞跃”,并非虚话。

根据测试芯片结果,他们预计RibbonFET晶体管带来的性能和密度提升,将超过当下的FinFET晶体管。而Intel 20A将是应用RibbonFET的第一枚芯片。

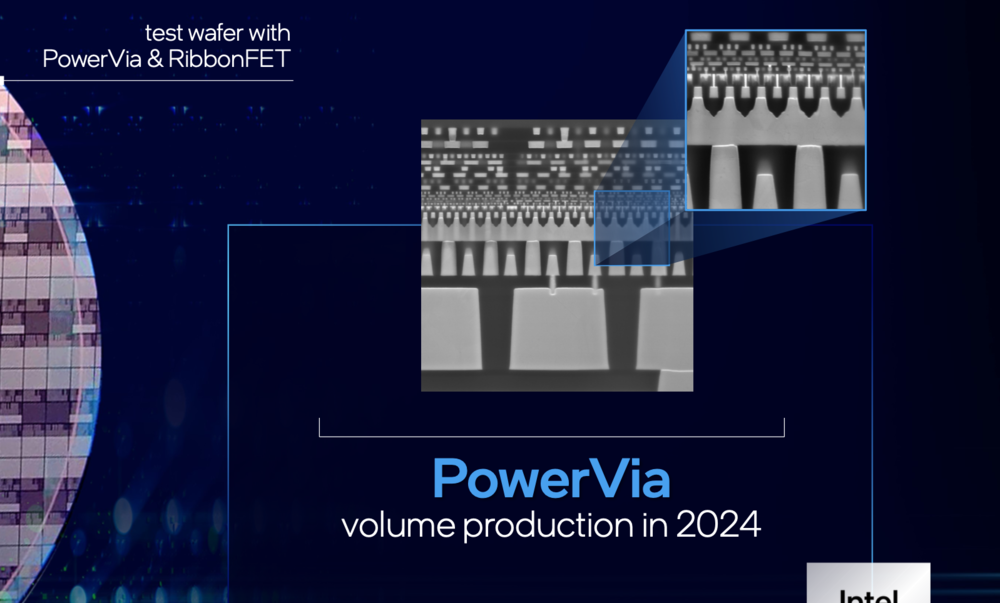

而电能传输系统PowerVia则是英特尔工程师开发的一项独特技术。Sanjay Natarajan博士作为这项技术的开发负责人,指出半导体晶体管结构中存在的最大传统问题之一便是“布线效率低下”。

“传统互连技术是在晶体管层的顶部进行互联,经常产生电源线和信号线的互混,导致了布线效率低下,进而影响性能和功耗。”

他们的解决方法,便是把电源线置于晶体管层的下面(也就是晶圆的背面)。通过减少晶圆正面的电源布线,腾出更多的“空地儿”用于优化信号布线,并减少时延,实现更好的电能传输。

值得注意的是,这两项将用于Intel20A的关键技术,虽然不可避免被人诟病为“仍然处于PPT状态”(毕竟还都是PPT),但英特尔的专家们展示了这些测试芯片的扫描电镜图像,显然经过了一系列测试。

就像上面所说,它们的成功应用,将决定着英特尔是否能在5nm这个关键节点上进行反超。

从时间来看,很明显,2019年时PPT上规划的“2023年实现7nm++”,与这次规划的“2024年实现Intel20A”没有多少间隔。也就是说,依然有机会在5nm这个节点上翻盘。

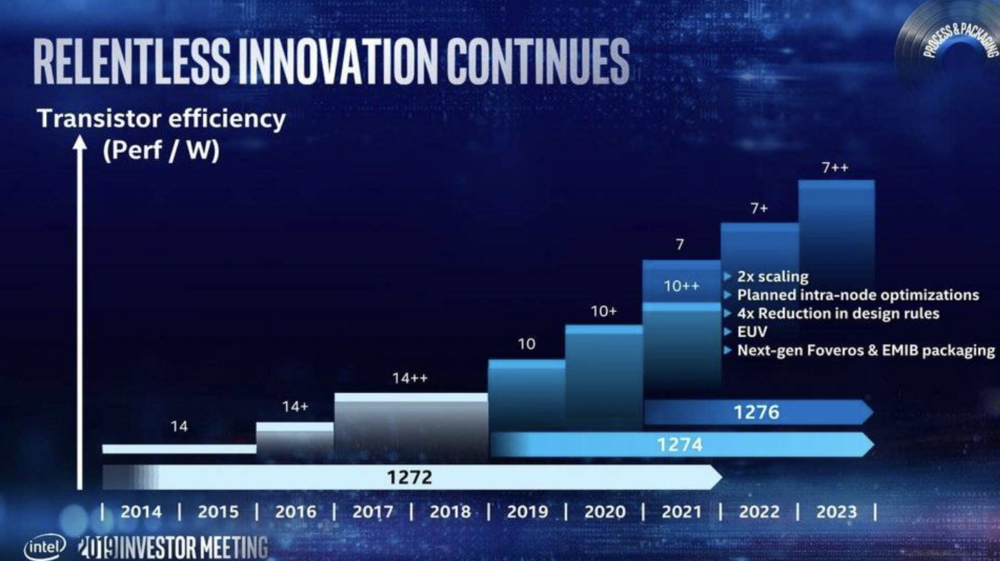

英特尔2019年10月的制程产品规划图

英特尔2019年10月的制程产品规划图

如基辛格所说,英特尔Intel20A在2024年的问世与两大关键技术的真正应用,将标志着半导体“埃米时代”(1埃米=0.1纳米)的启幕。

现在来听,其实更像是英特尔在向外界喊话:你们以为我还想在“纳米时代”争夺领导权?不,我们要进入一个比纳米更小的单位去争夺话语权了。

写在最后…希望不是PPT

但话说回来,既然完全改变了以纳米为单位的命名体系,而且晶体管结构和材料正在发生下一轮巨大变化。此外,英特尔也在从封装技术层面提高芯片的带宽密度和能效……

这一切难道不是意味着,所谓的纳米还是埃米的数字单位,已经越来越没意义了吗?

英特尔嘴上说在捍卫摩尔定律,其实已经认识到不能再依靠摩尔定律。

如今,Intel20A的制造工艺虽然官方说拿下了高通这个大订单,但距离2024年变数还有很大。我们虽然觉得英特尔这场发布会的意义重大,并且产品规划让人没有异议,但是PPT能够转变称真正的产品,还是需要实物说话。

毕竟,当年延迟了4年的14nm产品,当时PPT做的也挺不错的。